第一部分:VHDL核心概念与基础

问题1:什么是VHDL?它主要用于什么领域?

-

答案: VHDL(VHSIC Hardware Description Language,超高速集成电路硬件描述语言)是一种用于描述电子系统行为和结构的标准化语言,它主要用于数字电路的设计、仿真、综合和验证。

(图片来源网络,侵删)

(图片来源网络,侵删) -

解析:

- 硬件描述语言:它不像C或Java那样描述计算机的执行流程,而是描述硬件电路的结构(由哪些门电路构成)或行为(输入输出信号之间的逻辑关系)。

- 应用领域:

- 建模:创建从算法级到门电路级的系统模型。

- 仿真:在编写实际电路前,通过计算机模拟验证设计的逻辑功能是否正确。

- 综合:将VHDL代码自动转换成由基本逻辑门(与、或、非、触发器等)构成的网表,最终生成可以烧录到FPGA或ASIC中的配置文件。

- 文档:VHDL代码本身就是设计文档,清晰描述了电路的功能和接口。

问题2:一个最简单的VHDL设计文件(实体-结构体对)包含哪些基本部分?请举例说明。

-

答案: 一个最简单的VHDL设计文件包含两个核心部分:实体和结构体。

- 实体:定义设计的外部接口,包括输入、输出端口及其数据类型。

- 结构体:描述设计的内部逻辑功能或结构,即输入和输出信号之间的具体关系。

-

示例:设计一个2输入与门

-- 库声明:使用IEEE标准库 library IEEE; use IEEE.STD_LOGIC_1164.ALL; -- 实体:定义与门的输入输出端口 entity AND2_GATE is Port ( A : in STD_LOGIC; -- 输入端口A B : in STD_LOGIC; -- 输入端口B Y : out STD_LOGIC -- 输出端口Y ); end AND2_GATE; -- 结构体:描述与门的逻辑功能 architecture Behavioral of AND2_GATE is begin -- Y <= A and B; -- 这是一种描述方式(信号赋值) process(A, B) -- 这是另一种描述方式(进程) begin Y <= A and B; end process; end Behavioral; -

解析:

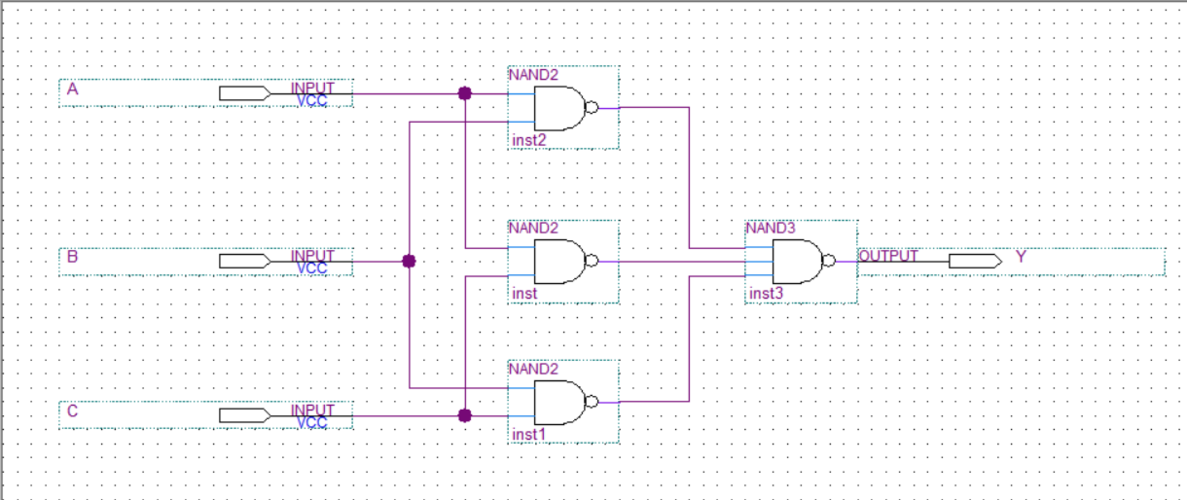

(图片来源网络,侵删)

(图片来源网络,侵删)library和use:引入标准库,使得可以使用STD_LOGIC等数据类型。entity ... is ... end entity:关键字,定义实体。Port子句是关键,声明了所有对外接口。architecture ... of ... is ... end architecture:关键字,定义结构体。of后面紧跟它所描述的实体名。STD_LOGIC:标准逻辑类型,可以表示'0', '1', 'Z'(高阻)等多种状态,比BIT类型更常用。

问题3:VHDL中的数据类型有哪些?STD_LOGIC和STD_LOGIC_VECTOR有什么区别和联系?

-

答案: VHDL有丰富的数据类型,主要分为标量类型和复合类型。

- 标量类型:

BIT:只能取'0'或'1'。STD_LOGIC:来自STD_LOGIC_1164包,是9值逻辑,包括 'U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-',更接近实际硬件,是首选。INTEGER:整数类型。BOOLEAN:布尔类型,TRUE/FALSE。

- 复合类型:

STD_LOGIC_VECTOR:一维数组,用于表示总线或多位数据。ARRAY:通用数组类型。

- 标量类型:

-

区别与联系:

- 区别:

STD_LOGIC表示单个信号线(1位)。STD_LOGIC_VECTOR表示一组信号线(多位),如一个8位的数据总线D_BUS : STD_LOGIC_VECTOR(7 downto 0);。

- 联系:

STD_LOGIC_VECTOR的每个元素都是一个STD_LOGIC类型。STD_LOGIC_VECTOR常用于表示地址总线、数据总线等,是数字系统设计中最常用的数据类型之一。

- 区别:

问题4:什么是进程?process语句的特点是什么?

-

答案:

process(进程)是VHDL中描述并行行为的基本单元,它包含一系列顺序执行的语句,但整个进程本身与其他所有进程都是并行执行的。 -

特点:

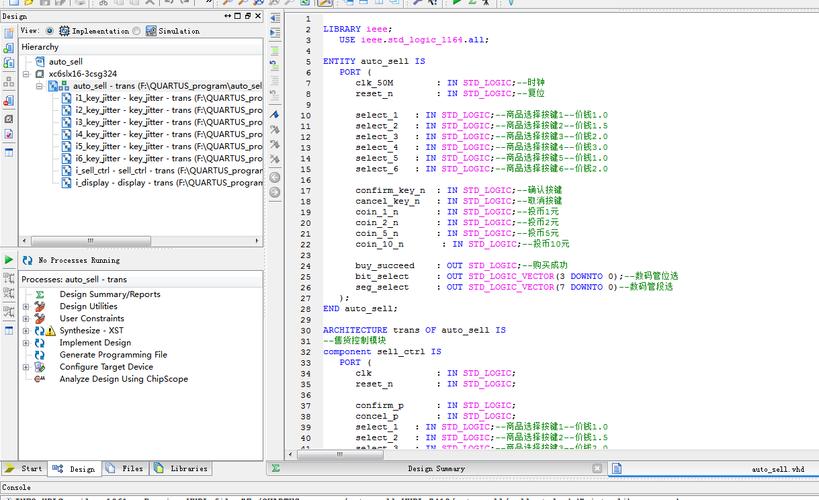

(图片来源网络,侵删)

(图片来源网络,侵删)- 并行性:一个设计中的多个

process语句是同时执行的,与它们在代码中的书写顺序无关。 - 顺序性:在

process语句内部,代码从上到下顺序执行,就像高级语言一样。 - 敏感信号列表:

process通常有一个敏感信号列表,如process(CLK, RST),当列表中的任何一个信号发生变化时,进程就会被激活,并从头开始执行。 - 无限循环:进程执行到末尾后,会自动回到开头,等待下一次被激活,一个进程会持续不断地运行,直到仿真结束。

- 并行性:一个设计中的多个

-

示例:带异步复位的D触发器

process(CLK, RST) -- 敏感列表包含CLK和RST begin if RST = '1' then -- 异步复位:RST优先级最高,与时钟无关 Q <= '0'; elsif rising_edge(CLK) then -- 时钟上升沿 Q <= D; end if; end process;

问题5:什么是信号和变量?它们有什么区别?

- 答案: 信号和变量都是用来存储数据的,但它们的赋值方式和行为有本质区别。

| 特性 | 信号 | 变量 |

|---|---|---|

| 硬件对应 | 物理上的连线和寄存器(如触发器输出) | 临时存储单元,通常综合为组合逻辑 |

| 赋值符号 | <= |

|

| 行为 | 赋值后,在下一个Δ时刻(仿真周期)才更新 | 赋值后,立即更新 |

| 作用域 | 在architecture级别声明,全局可见 |

在process, function, procedure内部声明,局部可见 |

| 使用场景 | 用于表示实体间的连接、状态寄存器、时钟信号 | 用于进程内的中间计算、临时结果存储 |

-

示例:理解赋值时机

signal A, B, C : STD_LOGIC; variable X, Y : STD_LOGIC; -- 在一个进程中 process(A) begin -- 信号赋值 B <= A; -- A的值变化后,B在下一个仿真周期才更新 C <= B; -- 此时B还是旧值,所以C会得到B的旧值 -- 变量赋值 X := A; -- X立即更新为A的新值 Y := X; -- Y立即更新为X的新值(即A的新值) end process;

第二部分:常用数字电路设计

问题6:如何用VHDL设计一个同步时序逻辑电路,比如4位计数器?

-

答案: 同步时序逻辑电路的特点是所有状态变化都在同一个时钟沿发生,设计时,通常在时钟进程的

rising_edge或falling_edge内部进行状态更新。 -

示例:4位同步加法计数器(带异步复位)

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.NUMERIC_STD.ALL; -- 使用numeric_std包进行整数运算 entity COUNTER_4BIT is Port ( CLK : in STD_LOGIC; -- 时钟 RST : in STD_LOGIC; -- 异步复位,高电平有效 COUNT: out STD_LOGIC_VECTOR(3 downto 0) -- 4位计数值输出 ); end COUNTER_4BIT; architecture Behavioral of COUNTER_4BIT is signal count_reg : UNSIGNED(3 downto 0); -- 内部计数寄存器,使用无符号类型更方便 begin process(CLK, RST) begin if RST = '1' then count_reg <= (others => '0'); -- 复位,计数器清零 elsif rising_edge(CLK) then count_reg <= count_reg + 1; -- 时钟上升沿,计数器加1 end if; end process; -- 将内部寄存器信号赋值到输出端口 COUNT <= STD_LOGIC_VECTOR(count_reg); end Behavioral; -

解析:

- 使用

UNSIGNED类型:NUMERIC_STD包中的UNSIGNED类型可以直接进行、等算术运算,非常方便。 - 内部信号

count_reg:用于存储当前计数值,综合后会生成4个触发器。 - 输出赋值:将内部寄存器的值转换为

STD_LOGIC_VECTOR再输出。

- 使用

问题7:如何设计一个有限状态机?

-

答案: 有限状态机是数字系统设计的核心,分为Moore型(输出仅与当前状态有关)和Mealy型(输出与当前状态和输入有关),VHDL中通常使用

case语句在进程中实现。 -

示例:一个简单的交通灯控制器(Moore型)

-- 定义枚举类型来表示状态 type STATE_TYPE is (RED, GREEN, YELLOW); signal current_state, next_state : STATE_TYPE; -- 主进程:状态寄存器 process(CLK, RST) begin if RST = '1' then current_state <= RED; elsif rising_edge(CLK) then current_state <= next_state; -- 状态在时钟边沿更新 end if; end process; -- 组合逻辑进程:根据当前状态和输入决定下一状态和输出 process(current_state) -- Mealy型会加入输入信号到敏感列表 begin case current_state is when RED => next_state <= GREEN; -- 输出信号 assignment... when GREEN => next_state <= YELLOW; -- 输出信号 assignment... when YELLOW => next_state <= RED; -- 输出信号 assignment... when others => next_state <= RED; end case; end process; -

解析:

- 状态编码:使用

type定义枚举类型是VHDL中描述FSM最清晰、最推荐的方式,综合工具会自动将其编码为二进制。 - 双进程法:将FSM分为状态寄存器进程(同步,描述状态如何转移)和组合逻辑进程(异步,描述下一状态和输出逻辑),这是最规范、最易读的写法。

others分支:用于处理未定义的状态,提高设计的健壮性。

- 状态编码:使用

问题8:什么是组件和配置?它们有什么用?

-

答案:

- 组件:是一个预先设计好的VHDL实体-结构体对的“声明”或“模板”,它允许你在一个更大的设计中像搭积木一样实例化(调用)其他已经设计好的模块。

- 配置:是VHDL的一个独特特性,它用于将一个实体绑定到一个特定的结构体,当同一个实体有多个结构体(如行为级、RTL级、门级)时,配置可以决定在顶层设计中具体使用哪一个。

-

作用:

- 组件:实现层次化设计,使复杂系统模块化,便于团队协作和复用。

- 配置:实现设计管理和多模型仿真,可以先使用行为级模型进行快速功能仿真,再用RTL级模型进行时序分析,最后用门级模型进行最终验证。

-

示例:使用组件实例化一个2选1多路选择器

-- 1. 首先声明组件(Mux2to1.vhd中已有) component Mux2to1 Port ( A, B, S : in STD_LOGIC; Y : out STD_LOGIC); end component; -- 2. 在顶层设计中实例化该组件 entity TOP_LEVEL is end TOP_LEVEL; architecture Structural of TOP_LEVEL is signal in1, in2, sel, out1 : STD_LOGIC; begin -- 实例化Mux2to1,并连接端口 U1: Mux2to1 port map ( A => in1, B => in2, S => sel, Y => out1 ); end Structural;

第三部分:高级主题与最佳实践

问题9:什么是综合?不可综合的VHDL代码有哪些常见例子?

-

答案: 综合是将高级的、行为级的VHDL代码自动转换成由基本逻辑门、触发器等硬件原语构成的门级网表的过程,只有可综合的代码才能被工具(如Vivado, Quartus, Synplify)转化为实际的硬件电路。

-

不可综合的VHDL代码常见例子:

- 文件I/O操作:如

READ,WRITE,这些是仿真命令,硬件无法打开文件。 - 某些数据类型:如

REAL(浮点数)、TIME(时间类型),除非使用特定的IP核,否则直接综合会很困难。 wait语句:在进程外部使用wait for 10 ns;是仿真命令,不可综合。after和transport:用于仿真中的延迟建模,如Y <= A after 5 ns;,实际硬件延迟由物理特性决定,不能这样精确指定。for...generate循环中的变量:在生成语句中,循环变量必须是integer类型,并且范围必须是静态已知的。- 复杂的算法:如某些复杂的数学函数、动态内存分配等,可能需要特定的IP核或状态机来实现,而不是直接用高级语言风格编写。

- 文件I/O操作:如

问题10:VHDL设计的“黄金法则”或最佳实践是什么?

- 答案:

为了写出清晰、高效、可综合、可维护的VHDL代码,应遵循以下最佳实践:

- 同步设计原则:尽量使用同步时序逻辑,所有状态变化都在统一的时钟沿发生,避免使用锁存器(latch)。

- 清晰的代码风格:

- 使用有意义的实体、信号、变量名。

- 添加充分的注释,解释设计的意图和复杂逻辑。

- 使用

STD_LOGIC_1164和NUMERIC_STD标准库。

- 避免使用锁存器:在组合逻辑中,如果

case语句或if语句没有覆盖所有可能性(缺少else或when others),综合工具会推断出锁存器,锁存器通常会导致时序问题和不稳定的设计,应尽量避免。 - 使用

case语句描述多路选择和FSM:case语句比if-elsif链更适合描述并行条件,综合效果好。 - 将设计划分为独立的、可复用的模块:使用组件实例化和层次化设计。

- 使用

unsigned和signed进行算术运算:避免直接对STD_LOGIC_VECTOR进行算术操作,使用NUMERIC_STD包更安全、更符合硬件思维。 - 在顶层进行I/O约束:将FPGA的引脚分配和时序约束放在专门的约束文件(如XDC)中,而不是VHDL代码里。

希望这份详细的“答案”能对您的VHDL学习之路有所帮助!学习VHDL的关键在于多写、多练、多思考,将代码与实际的硬件结构联系起来。