这本书作为一本经典的教材,通常不提供官方的、完整的“习题答案”,这是为了鼓励学生独立思考、自主完成作业,从而真正掌握EDA(电子设计自动化)技术。

别担心!虽然找不到官方的“标准答案”,但我们可以通过多种方式来获得帮助,并且我将为您提供一些关键章节的习题思路、核心知识点解析以及常见问题的解答方法。

如何获取学习帮助(推荐方法)

-

利用网络资源(首选)

- CSDN / 博客园 / 知乎:在这些平台上搜索书名+“答案”、“课后习题”、“解析”等关键词,很多学习者和老师会分享自己的解题过程和笔记。

- 百度文库 / 道客巴巴:这些文档分享网站上可能有学生上传的答案集或学习笔记,可以付费或免费下载,但请注意辨别答案的准确性。

- GitHub:搜索这本书,可能会有一些开源的学习项目或包含代码示例的仓库,虽然没有直接答案,但代码本身是最好的实践。

- 相关大学课程网站:许多高校开设了EDA相关课程,教师可能会在自己的课程页面上提供部分习题的解答或提示,可以搜索“EDA技术实用教程 课程大纲”或“课件”。

-

组建学习小组

和同学一起讨论难题,每个人对问题的理解角度不同,通过交流可以互相启发,共同进步,这是最有效、最深入的学习方式。

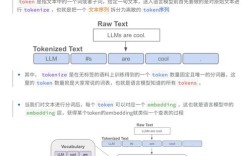

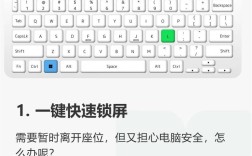

(图片来源网络,侵删)

(图片来源网络,侵删) -

请教老师或助教

这是最权威、最准确的方式,直接带着你的解题思路去请教老师,他们不仅能告诉你答案是否正确,还能指出你思路中的问题,帮助你建立正确的思维方式。

核心章节习题思路与知识点解析(第四版)

这里我将以第四版中几个核心章节为例,为你提供解题的思路和关键知识点,希望能帮你“授人以渔”。

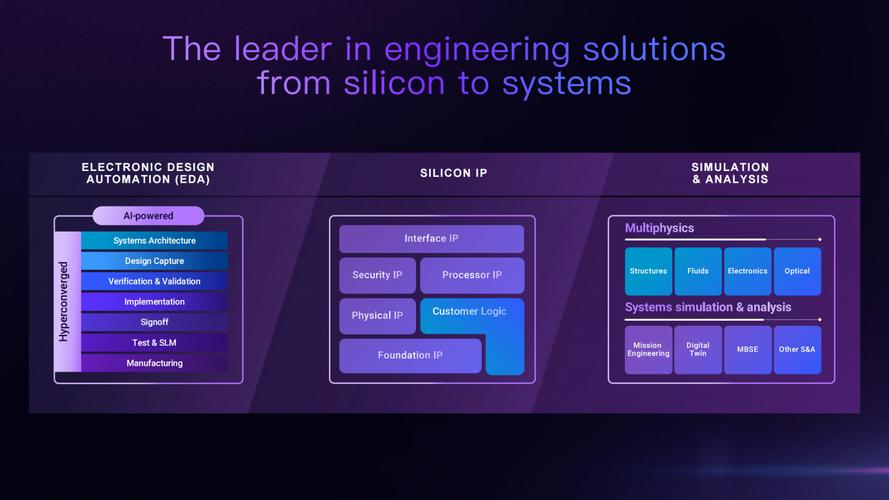

第1章 EDA技术概述

- 常见题型:简答题、填空题。

- 核心知识点:

- EDA的定义:利用计算机作为工作平台,融合应用电子技术、计算机技术、信息处理及智能化技术的最新成果进行电子系统设计的全过程。

- EDA技术的优势:设计效率高、可靠性高、可移植性好、技术保密性好、能实现大规模复杂电路设计。

- EDA设计流程:

- 设计输入:原理图输入、硬件描述语言输入。

- 综合:将高层次的HDL描述转化为由基本逻辑门(与、或、非等)构成的网表。

- 适配:将综合后的网表映射到特定的FPGA/CPLD芯片上,确定逻辑单元、引脚位置等。

- 仿真:功能仿真(验证逻辑正确性)和时序仿真(验证实际硬件性能)。

- 编程/配置:将最终生成的配置文件下载到FPGA/CPLD芯片中。

- 习题示例:

- 问:简述EDA技术的基本设计流程。

- 答:EDA技术的基本设计流程通常包括:① 设计输入:通过原理图或HDL语言描述电路;② 综合:将设计描述转换为门级网表;③ 适配:将网表映射到目标器件的逻辑结构中;④ 仿真:对设计进行功能仿真和时序仿真,验证其正确性;⑤ 编程/配置:将生成的配置文件下载到可编程器件中,完成硬件实现。

第2章 FPGA/CPLD结构原理

- 常见题型:填空题、选择题、简答题。

- 核心知识点:

- FPGA vs CPLD:

- CPLD:基于乘积项结构,是“与-或”阵列,内部逻辑资源丰富,适合实现复杂的组合逻辑和时序逻辑,但触发器资源相对较少,结构确定,时序可预测性好。

- FPGA:基于查找表结构,由大量的可配置逻辑块、输入/输出块和可编程连线构成,触发器资源丰富,适合时序逻辑和数据处理,结构灵活,但布线复杂,时序收敛性是设计难点。

- 查找表:FPGA的基本逻辑单元,一个N输入的LUT实际上是一个2^N位的SRAM,存储了该输入组合对应的输出真值表,一个2输入LUT可以实现任何2输入的逻辑功能。

- 可编程互连资源:用于连接CLB、IOB和块RAM等,实现复杂的布线。

- FPGA vs CPLD:

- 习题示例:

- 问:比较FPGA和CPLD在结构上的主要区别。

- 答:主要区别在于:

- 基本逻辑单元:CPLD基于乘积项结构,而FPGA基于查找表结构。

- 集成度:FPGA的集成度通常比CPLD更高,可以实现更复杂的系统。

- 触发器资源:FPGA拥有丰富的触发器资源,而CPLD的触发器资源相对较少。

- 连续布线:CPLD具有连续式互连结构,时序延迟可预测;FPGA采用分段式互连结构,布线更灵活但时序收敛性是挑战。

- 应用领域:CPLD适合 glue logic(胶合逻辑)、总线接口等中小规模逻辑;FPGA适合数字信号处理、高速接口、复杂状态机等大规模时序逻辑应用。

第3章 VHDL设计入门

-

常见题型:程序分析题、程序填空题、简答题。

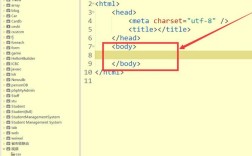

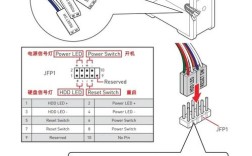

(图片来源网络,侵删)

(图片来源网络,侵删) -

核心知识点:

- VHDL基本结构:实体 + 结构体,实体定义端口,结构体实现功能。

- 数据类型:

std_logic,std_logic_vector,bit,integer等,注意std_logic和std_logic_vector的库声明。 - 并发语句:

process,when-else,with-select-when等。process语句是最重要的,其内部是顺序执行的。 - 顺序语句:

if-then-else,case-when,loop等,只能在process或function/procedure中使用。 - 进程敏感表:

process后面的括号内是敏感信号列表,当其中任何一个信号发生变化时,进程被激活。

-

习题示例:

- 问:分析下面VHDL代码,描述其功能。

library IEEE; use IEEE.STD_LOGIC_1164.ALL;

entity decoder_2to4 is Port ( en : in STD_LOGIC; a : in STD_LOGIC_VECTOR (1 downto 0); y : out STD_LOGIC_VECTOR (3 downto 0)); end decoder_2to4;

architecture Behavioral of decoder_2to4 is begin process(en, a) begin if en = '1' then case a is when "00" => y <= "0001"; when "01" => y <= "0010"; when "10" => y <= "0100"; when "11" => y <= "1000"; when others => y <= "0000"; end case; else y <= "0000"; end if; end process; end Behavioral;

* **答**:这是一个2-to-4线译码器,带有使能端。 * **功能**:当使能信号`en`为高电平'1'时,根据2位输入`a`的值,在4位输出`y`中对应的位置输出高电平'1'(低有效为'0'),当`a="01"`时,`y="0010"`,当使能信号`en`为低电平'0'时,输出`y`全为"0000",译码器被禁止。 - 问:分析下面VHDL代码,描述其功能。

第4章 Quartus II开发流程

- 常见题型:简答题、操作题。

- 核心知识点:

- Quartus II开发流程:

- 工程创建:指定工程名称、目标器件、EDA工具等。

- 设计输入:新建VHDL/Verilog文件或原理图文件。

- 编译:执行

Processing -> Start Compilation,综合、适配、时序分析都在此步骤中完成。 - 仿真:使用

Tools -> Launch EDA Simulation Tool或内置的仿真器进行功能仿真和时序仿真。 - 引脚分配:在

Assignments -> Pin Planner中为设计的端口分配具体的物理引脚。 - 编程/配置:使用

Tools -> Programmer将生成的.sof或.pof文件下载到FPGA开发板。

- Quartus II开发流程:

- 习题示例:

- 问:简述在Quartus II中完成一个VHDL设计并进行仿真的主要步骤。

- 答:

- 新建工程:打开Quartus II,使用

New Project Wizard创建新工程,选择合适的FPGA器件。 - 添加文件:将编写的VHDL源文件(

.vhd)添加到工程中。 - 编译设置:指定器件型号,进行编译设置。

- 全编译:执行

Start Compilation,检查设计是否有错误。 - 创建向量波形文件:新建

Vector Waveform File (.vwf),添加需要观察的输入/输出节点,并设置输入激励信号。 - 运行仿真:设置仿真器为

Functional(功能仿真),运行仿真,观察输出波形是否符合预期逻辑。

- 新建工程:打开Quartus II,使用

总结与建议

- 理解优于记忆:EDA技术是一门实践性很强的学科,不要死记硬背答案,要理解每个步骤背后的原理,理解了

process和case语句的执行机制,你就能写出任何你想要的组合逻辑。 - 动手实践是王道:一定要亲自在Quartus II或Vivado等软件中敲代码、建工程、做仿真、下载到板子上运行,亲手操作一遍,远比看十遍答案更有用。

- 善用工具:Quartus II和Vivado等工具本身就是最好的老师,学会看编译报告(特别是时序分析报告)、使用SignalTap II(嵌入式逻辑分析仪)进行实时调试,这些技能比单纯做对一道题更重要。

希望这份详细的指南能对你的学习有所帮助,祝你学习顺利,在EDA的世界里探索愉快!如果你有具体章节或具体问题,欢迎随时提出,我们可以进一步探讨。