Cadence 16.3 全流程设计教程 (以CMOS反相器为例)

第一部分:准备工作与环境设置

在开始之前,请确保您已经安装了 Cadence 16.3 版本,并配置好了必要的库文件(tsmc18 或 gf180mcu 等工艺库)。

(图片来源网络,侵删)

启动 Cadence

- 在终端中输入命令:

icfb & - 这会启动 Cadence 的图形用户界面。

设置工作目录

- 创建一个专门用于本次实验的文件夹,

~/cadence_lab/inverter。 - 在 Cadence 界面中,通过

File -> Change Directory将工作目录切换到该文件夹,所有生成的文件都会保存在这里。

创建库

- 在 CIW (Command Interpreter Window) 窗口中,点击

File -> New -> Library。 - Name: 输入库名,

my_lib。 - Technology Library: 选择

Attach to an existing techfile。 - Techfile Name: 点击

Browse,选择您工艺库对应的.tf文件(tsmc18.tf)。 - 点击

OK,这样,您的库就与特定的工艺技术关联起来了。

创建单元格

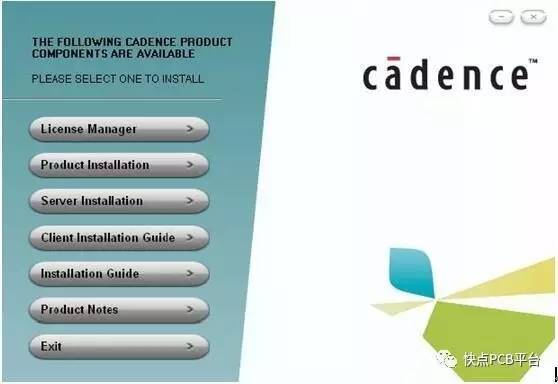

(图片来源网络,侵删)

- 在库管理器中,右键点击

my_lib,选择New -> Cellview -> From Cellview。 - Cell Name: 输入

inverter。 - View Name: 输入

schematic。 - Tool: 选择

Virtuoso Schematic Editor。 - 点击

OK,此时会打开一个空的原理图编辑窗口。

第二部分:绘制电路原理图

我们将在 schematic 视图中绘制 CMOS 反相器的电路。

添加元器件

- 在原理图编辑窗口中,点击快捷键

b(Add Instance) 或点击菜单Instance -> Place Instance。 - 在弹出的 "Component Browser" 窗口中:

- Library: 选择您的工艺库,

tsmc18。 - Cell: 选择

nmos或pmos。 - View: 选择

symbol。

- Library: 选择您的工艺库,

- 在画布上点击放置一个 NMOS 和一个 PMOS。

添加电源和地

- 再次按

b键。 - 在 "Component Browser" 中:

- Library: 选择

analogLib(这是 Cadence 自带的模拟库,包含电源、地等基本元件)。 - Cell: 选择

vdd(电源)。 - View:

symbol。

- Library: 选择

- 放置一个

vdd和一个gnd(地)。

连接线路

- 按

w键 (Add Wire) 或点击菜单Wire -> Wire。 - 将

vdd连接到 PMOS 的漏极。 - 将 PMOS 的源极连接到 NMOS 的漏极,这个节点就是反相器的输出

out。 - 将 NMOS 的源极连接到

gnd。 - 将 PMOS 的栅极和 NMOS 的栅极连接在一起,这个节点就是反相器的输入

in。

添加端口

- 按

p键 (Add Pin) 或点击菜单Pin -> Pin。 - 添加两个

Pin:- 一个命名为

in,连接到输入节点。 - 另一个命名为

out,连接到输出节点。 - 确保

Pin的I/O Type设置为input和output。

- 一个命名为

设置元器件参数

- 双击任何一个 NMOS 或 PMOS 符号,会弹出其属性编辑窗口。

- Width (W) 和 Length (L): 根据工艺规则设置合适的尺寸,可以都设为

18u(180纳米)。 - 点击

OK保存,通常为了匹配,PMOS 的宽度会是 NMOS 的 2-3 倍,以获得相同的驱动能力。

保存并检查

- 按

Ctrl + S保存原理图。 - 按快捷键

q(Check and Save) 或点击菜单Design -> Check and Save。 - CIW 窗口没有报错,说明原理图绘制正确。

第三部分:电路仿真

我们使用 Cadence 自带的 spectre 仿真器进行仿真。

创建仿真配置文件

- 在原理图编辑窗口中,点击菜单

Launch -> ADE L(Analog Design Environment L),这将打开仿真器主界面。

设置仿真变量

- 在 ADE L 界面中,点击

Setup -> Model Libraries。 - 在弹出的窗口中,点击

Browse,选择您工艺库的模型文件 (通常是.scs或.sp文件),然后点击Add和OK。

设置仿真分析

- 在 ADE L 界面中,点击

Analyses -> Choose。 - 勾选

tran(瞬态分析)。 - Stop Time: 设置为

10n(10纳秒)。 - 点击

OK。

设置变量

- 在 ADE L 界面中,点击

Variables -> Copy from Cellview,这会自动将原理图中的in和out端口作为变量添加进来。

设置输出波形

- 在 ADE L 界面中,点击

Outputs -> To Be Plotted -> Select on Schematic。 - 回到原理图窗口,分别点击

in和out节点,它们会出现在 ADE L 界面的 "Outputs" 列表中。

运行仿真

- 在 ADE L 界面中,点击绿色的运行按钮 (或按

F5)。 - 仿真结束后,会自动弹出 Waveform Viewer 窗口,显示

in和out的波形。

验证结果

- 你应该能看到一个标准的反相器波形:当输入

in为高电平时,输出out为低电平;当输入in为低电平时,输出out为高电平。

第四部分:版图设计与验证

原理图仿真通过后,我们开始进行物理版图的设计。

创建版图视图

- 关闭 ADE L 和 Waveform Viewer。

- 在库管理器中,右键点击

inverter单元,选择New -> Cellview。 - View Name: 输入

layout。 - Tool: 选择

Virtuoso Layout Editor。 - 点击

OK,此时会打开一个空的版图编辑窗口。

设置版图层

- 在版图编辑窗口中,点击菜单

Options -> Display。 - 在 "Layers" 标签页中,确保

nwell,pwell,pdiff,ndiff,poly,metal1,via1,metal2等工艺所需的关键层都已显示并设置了不同的颜色。

绘制版图

- 绘制阱区:

- 按

s键 (Shape)。 - 在 "Layer" 窗口中选择

nwell,在画布上画一个矩形包裹住 PMOS。 - 再画一个

pwell矩形包裹住 NMOS,注意阱区的间距规则。

- 按

- 绘制有源区:

- 选择

pdiff层,在nwell内画一个矩形作为 PMOS 的源漏区。 - 选择

ndiff层,在pwell内画一个矩形作为 NMOS 的源漏区。

- 选择

- 绘制多晶硅栅极:

- 选择

poly层,画一个横跨在ndiff和pdiff上方的矩形,将两个晶体管连接起来,形成反相器的输入。

- 选择

- 绘制接触孔:

- 选择

via1层,在有源区和多晶硅上放置接触孔,用于连接金属1。 - 在

pdiff上方放一个via1连接到vdd。 - 在

ndiff上方放一个via1连接到gnd。 - 在输入多晶硅两端各放一个

via1连接到metal1。 - 在输出节点 (

ndiff和pdiff的连接处) 放一个via1连接到metal1。

- 选择

- 绘制金属连线:

- 选择

metal1层。 - 用

metal1连接vdd接触孔到 PMOS 源极。 - 用

metal1连接gnd接触孔到 NMOS 源极。 - 用

metal1连接输入端的via1。 - 用

metal1连接输出端的via1。

- 选择

- 添加 I/O 端口:

- 点击菜单

Pin -> Pin。 - 在

Layer窗口中选择metal1。 - 在

vdd、gnd、in、out的金属上放置Pin,并命名。

- 点击菜单

保存并检查 DRC

- 按

Ctrl + S保存版图。 - 在版图编辑窗口中,点击菜单

Verification -> DRC...。 - 在弹出的窗口中,点击

Run。 - 检查 CIW 窗口:如果没有任何错误信息,说明版图通过了设计规则检查,如果有错误,根据提示修改版图。

第五部分:版图与原理图对比

确保版图实现的功能与原理图完全一致。

启动 LVS

- 在版图编辑窗口中,点击菜单

Verification -> LVS...。 - 在弹出的窗口中:

- Source: 选择

Layout。 - Netlist: 点击

Browse,选择当前版图对应的inverter(layout) 视图。 - Source: 选择

Schematic。 - Netlist: 点击

Browse,选择inverter(schematic) 视图。

- Source: 选择

- 点击

Run。

检查 LVS 结果

- 检查 CIW 窗口:LVS 成功,会显示

LVS comparison successful,这意味着版图和原理图在拓扑结构上是完全一致的。 - 如果失败,CIW 会给出详细的错误信息,

Netlist comparison failed,你需要根据提示对比版图和原理图,找出连接错误或元器件不匹配的地方。

第六部分:生成网表与后仿真

生成版图网表

- 在 LVS 窗口中,点击

Extract按钮。 - 这会生成一个包含寄生参数的版图网表文件 (

.sp或.scs格式)。

运行后仿真

- 回到 ADE L 界面 (

Launch -> ADE L)。 - 加载寄生参数: 在 ADE L 中,点击

Setup -> Model Libraries,将刚刚生成的版图网表文件添加进去。 - 运行仿真: 再次运行瞬态仿真 (

tran)。 - 对比波形: 对比后仿真波形和之前的原理图仿真波形,你会发现后仿真的波形会有延迟和失真,这是因为版图中的寄生电阻和电容效应,这个延迟就是电路的实际延迟。

总结与后续

恭喜!您已经完成了一个完整的 Cadence 16.3 设计流程,包括:

- 原理图设计

- 前仿真

- 版图设计

- DRC/LVS 验证

- 后仿真

这个流程是所有模拟和混合信号集成电路设计的基础,您可以在此基础上,尝试设计更复杂的电路,如与非门、或非门、运算放大器等。

进阶提示:

- 参数化单元: 使用

pcell功能可以创建可配置的版图单元,提高设计效率。 - 约束驱动布局: 在版图布局前,先定义时序、功耗等约束,让工具辅助完成布局。

- 寄生参数提取: 学习更高级的寄生提取工具,如

StarRC,以获得更精确的 RC 网表。 - 时序分析: 学习使用

TimeQuest等静态时序分析工具进行数字电路的时序验证。

希望这份详细的教程能帮助您顺利入门 Cadence!