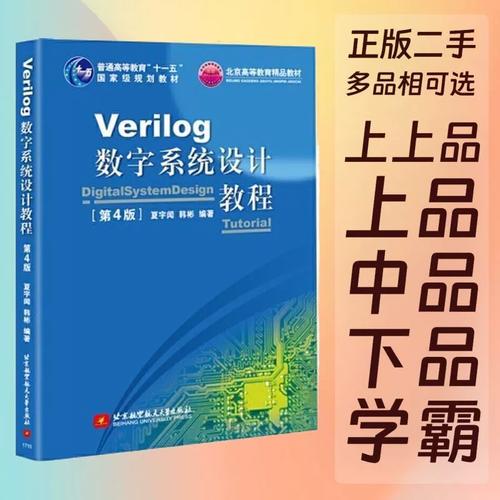

书籍核心信息

- 书名: Verilog数字设计教程

- 作者: 夏宇闻

- 出版社: 北京航空航天大学出版社

- 地位: Verilog语言学习领域的经典之作,国内高校最广泛采用的教材之一。

为什么这本书如此经典和受欢迎?

这本书的成功并非偶然,它完美地契合了初学者的学习路径和思维模式,具有以下几大核心优点:

循序渐进,由浅入深,符合认知规律

这是本书最大的优点,夏宇闻教授深谙教学之道,他没有一上来就抛出复杂的语法和概念。

- 从“门”开始: 书的前半部分从最基本的逻辑门(与、或、非)和组合逻辑电路(编码器、译码器、多路选择器)讲起,用Verilog语言去描述这些你已经知道的硬件电路,让你建立起“代码即电路”的直观认识。

- 逐步引入语法: 在你对基本组合电路的描述有感觉后,才逐步引入

assign语句、always块、if-else、case等核心语法,这种“先实践,后理论”的方式,让语法不再是枯燥的规则,而是实现特定功能的工具。 - 从组合到时序: 清晰地划分了组合逻辑和时序逻辑(触发器、寄存器、计数器、状态机)的学习模块,让你能系统地掌握数字设计的两大基石。

强调“设计思维”,而非“语法手册”

很多Verilog书籍只是简单地罗列语法,但夏宇闻教授的教程重在培养硬件描述语言的设计思维。

- 代码即硬件: 书中反复强调,Verilog代码不是软件程序,它是对硬件电路结构的描述,代码写得好不好,最终要看它综合出的电路是否高效、可靠,这种思维方式的建立,是区分“Verilog程序员”和“数字设计师”的关键。

- 关注可综合性: 书中的大量示例都是可综合的,即这些代码可以被EDA工具(如Synopsys DC, Vivado, Quartus)直接翻译成实际的硬件电路,这让你从一开始就写出能落地的代码,而不是停留在仿真验证阶段。

示例丰富且经典,贴近实际应用

书中包含了大量精心挑选和编写的实例,这些例子覆盖了数字设计的方方面面:

- 基础模块: 加法器、比较器、译码器等。

- 核心时序逻辑: 计数器、移位寄存器。

- 设计精髓: 有限状态机 是本书的重中之重,用了大量篇幅进行讲解,从Moore型到Mealy型,从状态编码到设计技巧,讲解得非常透彻。

- 完整系统: 书的结尾通常会包含一些小型数字系统设计的例子,如UART、CPU模型等,让你能将所学知识融会贯通,体验从零开始构建一个复杂系统的过程。

语言风格平实易懂,适合自学

夏宇闻教授的行文风格非常朴实,没有过多的晦涩理论,而是用通俗易懂的语言把复杂的概念讲清楚,对于自学者来说,这本书的可读性非常高,就像一位经验丰富的老师在手把手地指导你。

书籍的潜在缺点与学习建议

虽然这本书非常经典,但在今天看来,也存在一些局限性,学习时需要注意:

局限性

- Verilog-1995为主: 这本书主要基于Verilog-1995标准,虽然语法核心是通用的,但对于现代设计更推荐的Verilog-2001(如

generate语句、always @(*)等)和SystemVerilog(接口、断言、随机化等高级特性)涉及较少,现代工业界和学术界已经广泛使用SystemVerilog。 - 工具链相对陈旧: 书中使用的仿真工具(如早期的ModelSim)和综合工具示例,与当前主流的Vivado, Quartus Prime等工具在界面和流程上有所不同,但这不影响核心设计思想的掌握。

- 侧重RTL设计,验证部分较弱: 作为一本“设计”教程,其对SystemVerilog验证方法学(如UVM)的介绍几乎没有,学习验证需要另外参考专门的书籍。

如何高效学习这本书?

- 动手,动手,再动手: 数字设计是实践性极强的学科。千万不要只看不练! 书中的每一个例子,无论大小,都必须亲手输入、仿真、综合,观察波形,理解代码和电路之间的对应关系。

- 理论与实践结合: 学习每个章节时,先回顾一下数字电路的基础知识(学计数器前,先想清楚异步/同步计数器的原理和区别),这样学Verilog会事半功倍。

- 仿真工具是必备的: 安装一个现代的EDA工具,如Vivado(免费版功能足够学习)或Quartus Prime,利用其自带的仿真器(如Vivado的Simulator)进行波形分析,这是验证设计正确性的唯一途径。

- 补充SystemVerilog知识: 在学完本书打下坚实基础后,强烈建议学习SystemVerilog,可以阅读《SystemVerilog验证:测试平台编写指南》或相关课程,以跟上行业发展的步伐。

- 结合在线资源: B站、YouTube等平台有大量基于此书的视频教程,可以帮助你更好地理解难点。

《Verilog数字设计教程》是一本无可争议的、顶级的入门教材。

- 如果你是初学者,这本书是你的最佳选择,它能帮你打下最坚实、最正确的基础,培养宝贵的硬件设计思维。

- 如果你有一定基础,想回顾和巩固,这本书依然是绝佳的参考,它的讲解方式和经典案例会让你受益匪浅。

学习路径建议: 《Verilog数字设计教程》 (打好RTL基础) → SystemVerilog/验证方法学 (提升实战能力) → 实际项目/开源项目 (积累经验)

夏宇闻教授的这本教程,是通往数字设计殿堂的一块坚实基石,只要你认真学习、勤于实践,必将为你未来的职业生涯打下坚实的基础。