本教程将以一个经典的 CMOS 反相器 设计为例,贯穿数字集成电路设计的完整流程,包括:

- 环境准备

- 设计输入

- 仿真验证

- 综合

- 物理设计

- 最终验证

重要提示:Cadence 版本与工具集

Cadence 是一个庞大的软件生态系统,不同公司、不同项目使用的工具组合可能不同,最核心、最通用的工具集是 Virtuoso (用于模拟/混合信号设计) 和 Genus/Innovus (用于数字后端设计)。

本教程将主要围绕这两个工具集展开,并解释其工作流程,在开始之前,请确保你已经:

- 安装了指定版本的 Cadence 工具。

- 获得了相应的许可证。

- 熟悉基本的 Linux 操作系统命令,因为 Cadence 主要在 Linux 环境下运行。

第一部分:准备工作

在开始任何设计之前,必须建立一个规范的项目目录结构,这能保证设计的可移植性和可维护性。

1 创建项目目录

打开 Linux 终端,创建一个主目录和子目录来存放不同阶段的设计文件。

# 创建主项目目录 mkdir my_inverter_project cd my_inverter_project # 创建子目录 mkdir design # 存放源代码文件 (如 Verilog, Spectre) mkdir sim # 存放仿真脚本和结果 (如 .log, .raw, .psf) mkdir syn # 存放综合后的网表和脚本 mkdir pnr # 存放布局布线后的文件 (如 .gds, .def)

2 设置环境变量

Cadence 需要一些环境变量来定位其安装路径、库文件等,公司或学校会提供一个 cdssetup 脚本或一个 tools.csh / tools.sh 文件。

# 假设 setup 文件在上级目录 source ../setup.csh # 或者 source ../setup.sh

运行后,你的终端提示符可能会改变,which 命令应该能找到 Cadence 的可执行文件。

3 准备工艺库文件

这是最关键的一步,你的设计必须基于一个特定的工艺技术(如 TSMC 28nm, GF 22nm 等)。

你需要从 foundry(如 TSMC)获取以下文件:

- 工艺设计套件:包含器件模型、设计规则、版图层次定义等。

- 标准单元库:包含预定义的逻辑门(如 NAND, NOR, Flip-Flop)的网表、时序信息、物理版图等。

- 技术文件:用于约束和仿真的文件。

将这些库文件解压并放置在一个固定的位置,/home/user/pdk/TSMC28,然后在你的脚本中通过环境变量(如 PDK_PATH)指向它。

第二部分:设计输入

我们将使用两种主流的设计方法:Verilog (数字) 和 Spectre (模拟)。

1 Verilog 数字设计

创建一个 design 目录下的 inverter.v 文件。

// design/inverter.v

module inverter (

input in,

output out

);

// 实例化一个反相器

// inv_1 是一个预定义在标准单元库中的单元名称

inv_1 my_inv (.in(in), .out(out));

endmodule

2 Spectre 模拟设计

对于模拟电路,我们使用 Cadence 的硬件描述语言 Spectre。

创建一个 design 目录下的 inverter.scs 文件。

// design/inverter.scs // Spectre netlist for a CMOS inverter // Include the model files from the PDK `include "path/to/pdk/models/corners/tt_models.scs" // Example for Typical-Typical corner // Circuit definition Xinv1 (in out) vdd gnd inv_1p8v_tt // X is for instance, inv_1p8v_tt is the cell name in the PDK // Power supplies vdd (vdd 0) dc 1.8 vss (gnd 0) dc 0 // Input source Vin (in 0) pulse(0 1.8 0 10p 10p 1n 2n) // Pulse from 0 to 1.8V, rise/fall 10ps, period 2ns // Analysis tran 1p 10n // Transient analysis from 0 to 10ns with 1ps step

注意:

Xinv1实例化的单元名称inv_1p8v_tt和模型文件的路径需要根据你的 PDK 实际情况修改。

第三部分:仿真验证

验证设计是否按预期工作。

1 数字仿真

数字仿真通常使用 VCS 或 Xcelium,这里以 VCS 为例。

-

编写编译脚本 (

sim/compile.sh)#!/bin/bash vcs -full64 -sverilog -timescale=1ns/1ps \ +incdir+../pdk/include \ ../design/inverter.v \ -o simv -

编写运行脚本 (

sim/run.sh)#!/bin/bash ./simv -vcd+ waves.vcd

-

执行仿真

cd sim chmod +x compile.sh run.sh ./compile.sh ./run.sh

-

查看波形

使用 Verdi 或 DVE 打开生成的

waves.vcd文件,检查输入in和输出out的波形是否正确(反相)。

2 模拟仿真

模拟仿真使用 Virtuoso。

-

启动 Virtuoso

在终端输入命令:

virtuoso &

-

创建 Cellview

- 在弹出的窗口中,选择

File -> New -> Cellview...。 - Library Name: 选择或创建一个库(

my_lib)。 - Cell Name:

inverter。 - View Name:

schematic。 - Tool:

Composer-Schematic。 - 点击

OK。

- 在弹出的窗口中,选择

-

绘制原理图

- 在左侧的库浏览器中,从你的 PDK 库中找到

nmos和pmos器件,拖放到画布上。 - 使用

Wire工具连接它们,构成一个反相器。 - 添加

vdd和gnd符号。 - 添加一个

Voltage Source作为输入激励。 - 添加

Net Name为输入和输出端口。

- 在左侧的库浏览器中,从你的 PDK 库中找到

-

设置仿真

- 在原理图窗口中,选择

Tools -> Simulation -> Environment...。 - 在

Simulator栏选择spectre。 - 在

Stop Time栏填入10n(10纳秒)。 - 点击

OK。

- 在原理图窗口中,选择

-

运行仿真

- 选择

Tools -> Simulation -> Netlist and Run。 - Virtuoso 会自动生成网表并启动仿真器,仿真结束后,会自动打开 Waveform Viewer 窗口。

- 选择

-

查看和分析波形

在 Waveform Viewer 中,添加

in和out信号,观察波形是否正确,你还可以使用Calculator工具进行更复杂的分析,如计算上升/下降时间、传播延迟等。

第四部分:综合

综合是将 RTL 代码(如 Verilog)自动转换为与工艺相关的门级网表的过程。

1 使用 Genus 进行综合

Genus 是 Cadence 的主流数字综合工具。

-

编写综合脚本 (

syn/synth.tcl)# Read the library and design read_liberty -min my_lib.lib # Min library for worst-case analysis read_liberty -max my_lib.lib # Max library for best-case analysis read_verilog ../design/inverter.v # Elaborate the design elaborate inverter # Apply constraints (e.g., clock period, input/output delays) create_clock -name clk -period 2 [get_ports clk] # Example: assume there's a clk port set_input_delay 0.5 -clock clk [all_inputs] set_output_delay 0.5 -clock clk [all_outputs] # Synthesize compile_ultra # Write out the netlist write_verilog -no_tri inverter_netlist.v

-

执行综合

cd syn genus -files synth.tcl

执行完成后,你将得到一个 inverter_netlist.v 文件,这个文件是针对特定工艺的、由标准单元组成的网表。

第五部分:物理设计

物理设计将门级网表转换为最终的版图,并确保设计满足时序、功耗和面积要求。

1 使用 Innovus 进行布局布线

Innovus 是 Cadence 的主流数字后端设计工具。

-

准备脚本 (

pnr/inno.tcl)# Read the design read_db ../syn/inverter_genus.db # Genus writes a .db file, this is better than .v # Floorplan initialize_floorplan # Add IO pins, core area, etc. # Place standard cells place_cells # Clock Tree Synthesis cts # Route the design global_route detail_route # Write output files write_gds inverter.gds write_def inverter.def write_sdf inverter.sdf

-

执行布局布线

cd pnr innovus -files inno.tcl

执行完成后,你将得到最终的版图文件:

inverter.gds: 用于芯片制造的图形数据格式。inverter.def: 描述了版图物理位置的交换数据格式。inverter.sdf: 标准延迟格式文件,用于后仿真。

第六部分:最终验证

在生成版图后,必须进行最终的验证,以确保版图与原始设计一致,并且满足所有设计规则。

1 LVS (Layout Versus Schematic) 检查

LVS 验证版图(GDS)是否与原理图(或综合后的网表)在电气连接上完全一致。

-

使用 Calibre 或 Diva:

- Diva 是 Virtuoso 自带的工具,相对简单。

- Calibre 是业界标准的物理验证工具,功能更强大。

-

LVS 流程 (以 Diva 为例):

- 在 Virtuoso 中打开版图 Cellview (

inverter - layout)。 - 运行

Verification -> LVS...。 - 指定原理图文件和版图文件,运行 LVS。

- 如果成功,会报告 "LVS Matched",如果不成功,会高亮显示不匹配的网线或器件,你需要手动修复。

- 在 Virtuoso 中打开版图 Cellview (

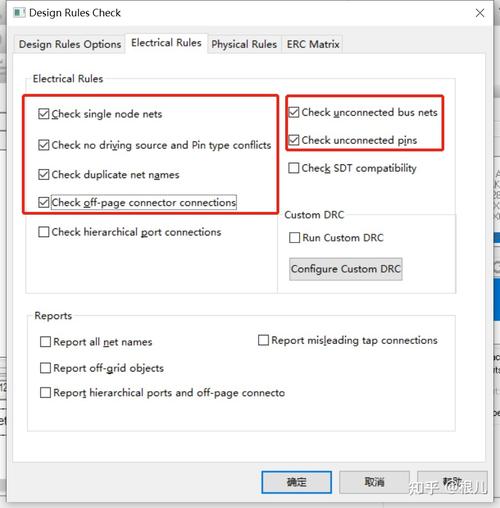

2 DRC (Design Rule Check) 检查

DVC 检查版图是否满足 foundry 提供的制造工艺规则(如线宽、间距、最小孔尺寸等)。

- 流程与 LVS 类似:

- 在 Virtuoso 中打开版图 Cellview。

- 运行

Verification -> DRC...。 - 选择相应的 DRC 规则文件(来自 PDK)。

- 运行 DRC。

- 如果失败,会标记出所有违反规则的地方,你需要根据错误提示进行修复,直到 "DRC Clean"。

总结与学习路径

| 阶段 | 核心工具 | 主要任务 | 输入文件 | 输出文件 |

|---|---|---|---|---|

| 设计输入 | Virtuoso, Text Editor | 绘制原理图或编写代码 | - | inverter.v, inverter.scs |

| 仿真验证 | VCS/Xcelium, Virtuoso | 功能验证,时序分析 | 设计文件 | waves.vcd, .log/.raw |

| 综合 | Genus | RTL -> 门级网表 | inverter.v, 标准单元库 |

inverter_netlist.v |

| 物理设计 | Innovus | 布局布线 | inverter_netlist.v |

inverter.gds, inverter.def |

| 最终验证 | Calibre/Diva | LVS, DRC | 版图, 原理图/网表 | LVS/DRC 报告 |

给初学者的建议

- 从模拟开始:如果你是电子工程背景,先从 Virtuoso 和 Spectre 仿真开始,因为它更直观,能帮助你理解半导体器件和电路行为。

- 找一个好导师/教程:Cadence 工具复杂,直接上手很容易迷失,跟着一个完整的例子(如本教程)走一遍是最好的学习方式。

- 理解底层原理:不要只做“点鼠标”的操作,要理解为什么需要 DRC/LVS,什么是 Setup/Hold Time,什么是 Clock Tree,工具只是实现你想法的手段。

- 多练习:尝试设计更复杂的电路,如与非门、D触发器、简单的加法器等,逐步建立信心。

希望这份详细的教程能帮助你顺利开启 Cadence 的学习之旅!祝你成功!