Altera (Intel) FPGA 综合学习教程

这份教程将按照“理论 -> 工具 -> 实践 -> 进阶”的路径,为你构建一个清晰的学习框架。

(图片来源网络,侵删)

第一部分:基础理论与准备

在开始动手之前,你需要理解一些核心概念,FPGA 的学习曲线相对陡峭,打好基础至关重要。

什么是 FPGA?

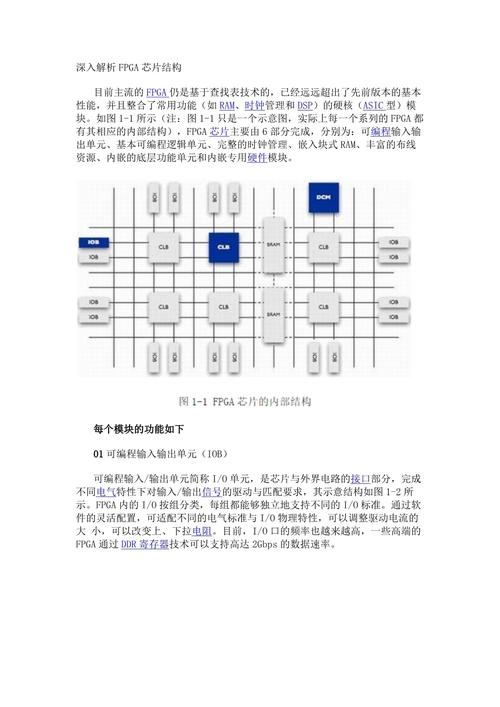

- 核心思想:与 ASIC(专用集成电路)不同,FPGA 是一种可编程的半导体器件,你可以通过配置,在 FPGA 内部搭建出你想要的数字电路(如 CPU、DSP、接口控制器等)。

- 基本结构:主要由可编程逻辑单元、输入/输出单元 和可编程互连资源 组成,数据通过查找表 来实现逻辑功能。

- 与 CPU 的区别:

- CPU:顺序执行指令,通过软件实现功能,擅长处理复杂的、串行的任务。

- FPGA:并行执行硬件电路,通过硬件描述语言 实现功能,擅长处理高吞吐量、低延迟的并行任务。

必备基础知识

- 数字电路:必须掌握!包括:

- 逻辑门(与、或、非、异或等)

- 布尔代数

- 组合逻辑电路(编码器、译码器、多路选择器等)

- 时序逻辑电路(触发器、寄存器、计数器、状态机)

- 数制与编码(二进制、十六进制、BCD 码)

- 硬件描述语言:这是描述 FPGA 电路的“代码”,主流有两种:

- Verilog HDL:语法类似 C 语言,上手相对快,业界使用广泛。

- VHDL:语法严谨,类似于 Ada 语言,在航空航天和军工领域更常见。

- 建议:初学者选择 Verilog,本教程将以 Verilog 为例,你不需要成为编程大师,但必须能用 HDL 描述出常见的数字逻辑。

开发环境准备

(图片来源网络,侵删)

- EDA 工具:FPGA 开发需要专门的软件,称为 EDA(电子设计自动化)工具。

- Intel Quartus Prime:这是 Intel 官方提供的、免费的 FPGA 开发套件。这是你必须要安装的软件。

- ModelSim / Questa Simulator:用于进行代码仿真,验证逻辑是否正确,Quartus Prime 中通常会集成一个免费版。

- 第三方工具:如 Synplify Pro (综合工具), Vivado (Xilinx 的工具,但了解其理念也有帮助)。

- 硬件平台:

- 开发板:强烈推荐初学者购买一块 Altera/Intel 官方的或第三方厂商的开发板,上面通常有 FPGA 芯片、LED、按键、数码管、串口、SDRAM 等外设,方便你进行实验。

- 入门级推荐:Intel Cyclone IV/V/10 GX 系列(如 DE0-Nano, DE10-Nano, Terasic DE10-Standard)的开发板,资料丰富,社区活跃。

- 下载器:USB-Blaster,用于将编译好的程序文件下载到 FPGA 芯片中。

- 开发板:强烈推荐初学者购买一块 Altera/Intel 官方的或第三方厂商的开发板,上面通常有 FPGA 芯片、LED、按键、数码管、串口、SDRAM 等外设,方便你进行实验。

第二部分:开发工具链详解

这是你的“武器库”,必须熟练掌握。

Intel Quartus Prime 工作流程 一个典型的 FPGA 项目开发流程如下:

graph TD

A[创建新项目] --> B[设计输入];

B --> C[设计综合];

C --> D[功能仿真];

D --> E[布局布线];

E --> F[时序仿真];

F --> G[生成编程文件];

G --> H[器件编程/下载];

Quartus Prime 详细步骤

-

创建新项目

(图片来源网络,侵删)

(图片来源网络,侵删)- 打开 Quartus Prime,选择

File -> New Project Wizard。 - 设置项目名称、保存路径、顶层实体名。

- 选择目标 FPGA 型号(DE10-Nano 上的

5CSEMA5F31C6)。 - 选择 EDA 工具(可以暂时都选 "None")。

- 完成创建。

- 打开 Quartus Prime,选择

-

设计输入

- 创建设计文件:

File -> New -> Verilog HDL File,保存为my_design.v。 - 编写代码:这是核心环节,编写一个简单的 LED 闪烁逻辑。

- 添加文件到项目:在

Project Navigator窗口中右键Files,选择Add/Remove Files in Project...,将你的.v文件添加进来。

- 创建设计文件:

-

分析与综合

- 点击

Processing -> Start Compilation。 - Quartus 会自动进行分析、综合 和适配。

- 综合:将你的 HDL 代码翻译成 Quartus 内部的基本门电路(LUT、FF 等)。

- 适配:将综合后的逻辑布局到 FPGA 芯片的具体物理位置上,并连接好布线线。

- 编译完成后,会生成报告,告诉你逻辑资源占用情况、时序是否满足要求等。

- 点击

-

仿真

- 目的:在硬件下载前,验证代码逻辑的正确性,检查时序是否违规。

- 创建测试台:

File -> New -> Vector Waveform File。 - 添加节点:在波形编辑器中,右键 ->

Insert -> Node or Signal...,将你的设计文件中的输入/输出信号添加进来。 - 设置激励:为输入信号(如时钟、复位)设置波形。

- 运行仿真:使用

Tools -> Run Simulation Tool -> RTL Simulation(功能仿真)或Gate-Level Simulation(时序仿真)。 - 查看结果:观察输出波形是否符合预期。

-

生成编程文件与下载

- 编译成功后,Quartus 会生成

.sof(SRAM Object File) 文件。 - 打开编程器:

Tools -> Programmer。 - 添加文件:点击

Add File...,选择.sof文件。 - 设置硬件:点击

Hardware Setup...,选择USB-Blaster。 - 开始编程:勾选文件,点击

Start,程序将被下载到 FPGA 中,硬件开始工作。

- 编译成功后,Quartus 会生成

第三部分:核心实践项目

理论结合实践,通过以下项目巩固你的知识。

项目 1:LED 闪烁器

-

目标:控制开发板上一个 LED 灯,以 1Hz 的频率闪烁。

-

知识点:

- 分频器:将 FPGA 的高速时钟(如 50MHz)分频到所需的低频(1Hz)。

- 寄存器:用于存储分频计数和 LED 的状态。

always @(posedge clk)块的使用。

-

Verilog 代码示例:

module blink_led ( input clk, // 50MHz clock input reset, // Active high reset output reg led // LED output ); // Counter to divide 50MHz to 1Hz reg [25:0] counter; // 2^26 is about 67 million, enough for 50MHz always @(posedge clk or posedge reset) begin if (reset) begin counter <= 26'd0; led <= 1'b0; end else begin if (counter == 26'd24_999_999) begin // 50,000,000 / 2 - 1 counter <= 26'd0; led <= ~led; // Toggle LED end else begin counter <= counter + 1'b1; end end end endmodule

项目 2:按键消抖

- 目标:按下开发板上的按键,能稳定地控制一个 LED 亮灭,避免因按键机械抖动导致的 LED 闪烁。

- 知识点:

- 同步:将异步的按键信号同步到系统时钟域。

- 状态机:设计一个简单的状态机来检测按键的“按下”和“释放”边沿。

- 滤波计数器:通过计数来滤除抖动噪声(通常持续 10-20ms)。

- 实现思路:

- 检测到按键按下后,启动一个计数器。

- 如果在计数期间按键一直保持按下状态,则认为按键稳定,输出有效信号。

- 如果中途按键释放,则复位计数器。

项目 3:数码管动态扫描显示

- 目标:在 4 位 7 段数码管上显示一个 4 位数字(如 1234)。

- 知识点:

- 多路复用/动态扫描:利用人眼的视觉暂留效应,快速轮流点亮每一位数码管。

- 译码器:将 BCD 码(0-9)转换为 7 段码(a-g)。

- 时分复用:分时控制位选和段选信号。

项目 4:UART 异步串口通信

- 目标:实现一个 UART 收发器,通过串口向 PC 发送数据,或接收 PC 发来的数据并显示在数码管上。

- 知识点:

- 帧格式:起始位、数据位、校验位(可选)、停止位。

- 波特率发生器:精确产生 UART 所需的时钟。

- 状态机:精确控制接收和发送的每个时序状态。

第四部分:进阶学习方向

当你掌握了以上基础后,可以探索更广阔的 FPGA 世界。

IP 核的使用

- 什么是 IP 核:Intel 提供的、经过验证的、可复用的硬件功能模块,如 Nios II (软核 CPU)、DDR SDRAM 控制器、PCIe 硬核、以太网 MAC 等。

- 如何使用:在 Quartus Prime 中使用

MegaWizard Plug-In Manager可以轻松配置和生成这些 IP 核。 - 意义:极大提高开发效率,避免重复造轮子,是实现复杂系统(如 SoC)的基础。

SoC (System on a Chip) 设计

- Nios II 处理器:这是 Intel FPGA 的软核处理器,学习如何将 Nios II 集成到你的 FPGA 设计中。

- Avalon 总线:连接 Nios II 及其外设(如 UART、定时器、PIO)的片上总线标准。

- 开发流程:

- 使用

Platform Designer(原 SOPC Builder) 创建包含 Nios II 及其外设的系统。 - 将生成的 HDL 顶层文件集成到 Quartus 项目中。

- 编写 C/C++ 程序,在 Nios II 集成开发环境 中进行软件开发和调试。

- 最终实现“硬件逻辑 + 软件程序”的协同工作。

- 使用

高级数字逻辑设计

- 状态机:深入学习 Moore/Mealy 状态机的设计与优化。

- FIFO (First-In, First-Out):用于数据缓冲和跨时钟域处理。

- 时钟域交叉:处理不同时钟域之间的数据传输问题,是高速设计的关键。

硬件加速与特定领域应用

- 图像处理:实现图像滤波、边缘检测等算法。

- 机器学习:利用 FPGA 的并行特性进行神经网络推理加速。

- 数字信号处理:实现 FIR/IIR 滤波器、FFT 等。

- 协议实现:如 PCIe, SATA, Ethernet 等。

推荐学习资源

-

官方文档 (最重要!)

- Intel 官网:https://www.intel.com/content/www/us/en/products/programmable.html

- Quartus Prime Handbook:官方的“圣经”,详细介绍了软件的每一个功能。

- IP 核用户指南:学习具体 IP 的官方文档。

-

开发板与教程

- Terasic (友晶科技):提供大量基于 Intel FPGA 的开发板(如 DE10-Nano, DE10-Standard),并附带了完整的实验手册和示例代码,是初学者的最佳选择。

- Intel FPGA University Program:为高校和学生提供免费的开发板和软件。

-

在线课程与社区

- Bilibili / YouTube:搜索 "FPGA Verilog 教程"、"Quartus Prime 教程",有很多优秀的中文和英文视频课程。

- FPGA 开发论坛:

- CSDN / 博客园:国内最大的开发者社区,有大量技术博客和问答。

- FPGA Forum (Intel 官方):https://community.intel.com/t5/Programmable/ct-p/design

- EEVblog Forum:国际知名的电子工程师论坛。

-

经典书籍

- 《Verilog HDL 高级数字设计》:深入理解 Verilog 语法和设计思想。

- 《FPGA 原理与设计入门》:系统介绍 FPGA 基础知识。

- 《数字设计和计算机体系结构》:结合 CPU 设计讲解数字逻辑,非常有深度。

学习建议总结:

- 动手为主,理论为辅:不要只看书,一定要亲手敲代码、做实验。

- 由简到繁:从 LED 闪烁开始,逐步挑战更复杂的项目。

- 善用仿真:养成先仿真、后下载的好习惯,能帮你快速定位问题。

- 阅读源码:多看别人的优秀设计,学习他们的思路和技巧。

- 保持耐心:FPGA 学习是一个漫长但回报丰厚的过程,遇到困难不要轻易放弃。

祝你学习顺利,早日成为 FPGA 高手!