电子电路怎么防静电(电子电路怎么防静电的)

电子电路的防静电措施是确保电子设备正常运行和延长其使用寿命的重要环节,静电不仅会导致电子元件损坏,还可能干扰整个电路系统,甚至引发数据丢失或系统崩溃,采取有效的防静电措施至关重要,以下是关于电子电路如何防静电的详细解答:

一、静电的产生与危害

静电是一种客观存在的自然现象,产生的方式多样,如接触、摩擦、电器间感应等,静电的特点是长时间积聚、高电压、低电量、小电流和作用时间短,人体自身的动作或与其他物体的接触、分离、摩擦或感应等因素,可以产生几千伏甚至上万伏的静电。

静电对电子设备的危害主要体现在以下几个方面:

穿透元器件内部薄的绝缘层:静电放电(ESD)可能穿透元器件内部的薄绝缘层,导致元器件损坏。

损毁MOSFET和CMOS元器件的栅极:MOSFET和CMOS器件的栅极对静电特别敏感,容易被静电击穿。

触发器锁死:CMOS器件中的触发器在静电作用下可能锁死,导致电路失效。

短路PN结:静电可能导致PN结短路,无论是反偏还是正偏状态。

熔化有源器件内部的焊接线或铝线:强静电可能导致器件内部的焊接线或铝线熔化。

二、防静电措施

针对静电的危害,可以采取以下多种技术手段进行防范:

1. 设计层面的防护

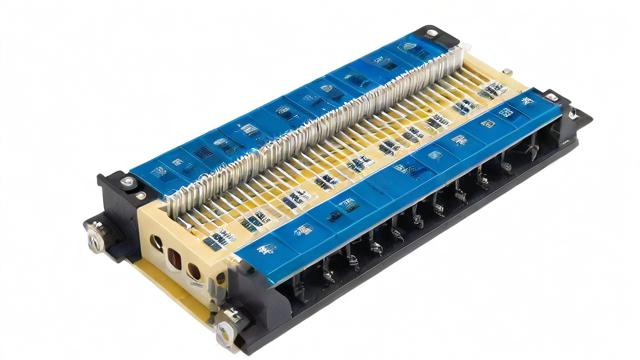

分层与布局布线调整:通过PCB板的分层设计和合理的布局布线,可以减小静电耦合效应,提高电路的抗ESD能力。

使用ESD保护电路:在设计中加入ESD保护电路,如雪崩二极管、高压电容、铁氧磁珠等,以快速响应并消耗静电能量。

雪崩二极管:并联于关键信号线上,利用其快速响应和稳定钳位能力保护电路板。

高压电容:放置在I/O连接器或关键信号位置,耐压至少为1.5KV,连接线尽量短以减小感抗。

铁氧磁珠:衰减ESD电流并抑制辐射。

火花间隙法:在铜皮构成的微带线层使用尖端相互对准的三角铜皮构成,尖端放电消耗电能。

LC滤波器:有效减小高频静电进入电路,电感抑制高频ESD,电容分流高频能量到地。

2. 结构与环境层面的防护

多层板设计:选择多层板设计,使ESD更快捷地耦合到低阻抗平面上,保护关键信号。

电路板外围留保护带:在电路板周围画出不加组焊层的走线,条件允许时连接至外壳,避免形成环形天线。

采用有钳位二极管的CMOS或TTL器件:利用隔离原理进行保护,减小设计复杂度。

增加去耦电容:使用低ESL和ESR数值的去耦电容,减小环路面积,滤除高频能量。

3. 操作与维护层面的防护

静电泄露与耗散:通过接地、增湿、屏蔽等手段将静电电荷引入地面或耗散掉。

人体静电防护:穿戴防静电手腕带、脚腕带、工作服、鞋袜、帽、手套或指套等,形成静电泄放、中和与屏蔽系统。

环境湿度控制:保持适宜的环境湿度(45%~65%),抑制静电的产生。

机房防静电地板:铺设防静电地板,迅速导入地面静电,避免积累。

焊接工具接地:使用接地的焊接工具,及时导入地面操作过程中产生的静电。

提高结构件绝缘能力并良好接地:减少静电产生和积累,确保所有结构件都良好接地。

电子电路的防静电措施是一个综合性的系统工程,需要从设计、结构、环境、操作等多个层面入手,通过合理的分层与布局布线、使用ESD保护电路、选择多层板设计、控制环境湿度、穿戴防静电装备以及提高结构件绝缘能力并良好接地等措施,可以有效地防止静电对电子设备的干扰和破坏,对于已经发生的静电损害,应及时进行检测和维修,以确保电子设备的正常运行。

四、相关问答FAQs

Q1: PCB板上常用的ESD保护电路有哪些?它们是如何工作的?

A1: PCB板上常用的ESD保护电路包括雪崩二极管、高压电容、铁氧磁珠、火花间隙法以及LC滤波器等,这些保护电路通过不同的机制来快速响应并消耗静电能量,雪崩二极管利用其快速响应和稳定钳位能力来保护电路;高压电容则通过耐高压特性来承受静电冲击;铁氧磁珠能够衰减ESD电流并抑制辐射;火花间隙法则是通过尖端放电来消耗电能;而LC滤波器则通过电感和电容的组合来减小高频静电进入电路。

Q2: 为什么多层板设计有助于提高电子电路的抗ESD能力?

A2: 多层板设计有助于提高电子电路的抗ESD能力,主要是因为多层板中有一个靠近走线的完整地平面,这个地平面使得ESD能够更快捷地耦合到低阻抗平面上,从而保护关键信号免受静电干扰,多层板的设计还可以提供更多的布线空间和更好的电磁兼容性能,进一步提高电路的整体稳定性和可靠性。

作者:豆面本文地址:https://www.jerry.net.cn/articals/4230.html发布于 2024-12-24 06:55:37

文章转载或复制请以超链接形式并注明出处杰瑞科技发展有限公司