如何绘制晶振电路原理图?

1、确定所需元件

晶振:根据电路需求选择合适的晶振频率,常见的有32.768kHz用于实时时钟,12MHz、24MHz等用于单片机系统。

电容:一般需要两个负载电容,其值根据晶振的频率和规格来确定,通常在15pF到30pF之间,如果使用有源晶振,可能还需要额外的去耦电容。

电阻:在某些情况下,可能需要添加匹配电阻来调整信号的传输特性,但并非所有晶振电路都需要。

其他元件:如电感、二极管等,用于电源滤波或信号处理等特定目的。

2、绘制晶振符号

在原理图中,晶振通常用一个特定的符号表示,对于无源晶振,它有两个引脚,一个连接到电源或地,另一个连接到微控制器的时钟输入引脚,对于有源晶振,它有四个引脚,除了电源和地引脚外,还有输出引脚和控制引脚(如果需要外部控制的话)。

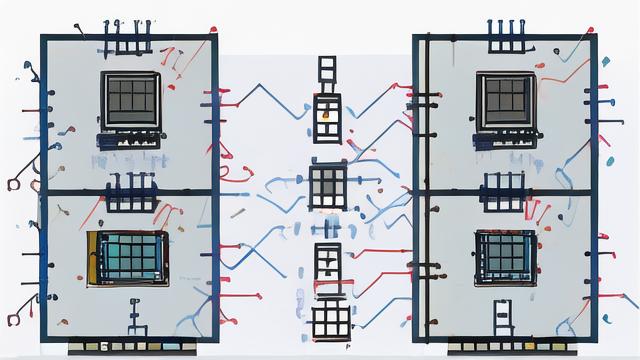

3、连接电路

将晶振的两个引脚分别连接到微控制器的相应引脚上,如果是无源晶振,其中一个引脚通过一个电容接地,另一个引脚连接到微控制器的时钟输入引脚,如果是有源晶振,将输出引脚连接到微控制器的时钟输入引脚,电源引脚连接到电源,接地引脚接地。

根据需要,在晶振的电源引脚和地之间添加去耦电容,以提高电源的稳定性,一个0.1uF的陶瓷电容和一个10uF的电解电容可以并联使用作为去耦电容。

如果使用了匹配电阻,将其放置在晶振的输出引脚和微控制器的时钟输入引脚之间。

4、检查和完善原理图

仔细检查所有的连接是否正确,确保没有短路或开路的情况。

标注各个元件的参数和引脚功能,以便后续的PCB布线和调试工作。

根据实际需要,可以在原理图中添加一些注释或说明,以增加可读性。

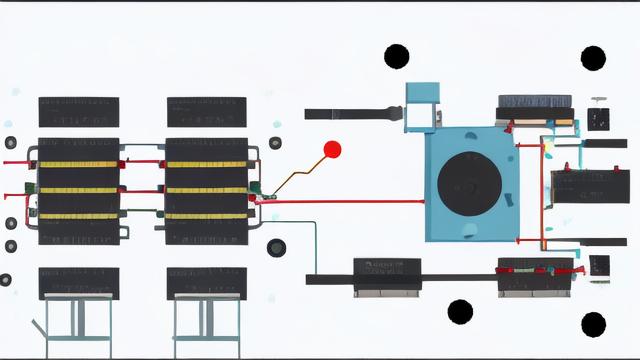

以下是一个简单的无源晶振电路原理图示例:

| 元件 | 连接方式 | 说明 |

| 无源晶振 | 1脚连接到微控制器的XTAL1引脚,2脚通过一个15pF的电容接地 | 提供稳定的时钟信号 |

| 电容 | 一端连接到无源晶振的2脚,另一端接地 | 与晶振共同构成谐振电路,稳定振荡频率 |

| 微控制器 | XTAL1引脚连接到无源晶振的1脚 | 接收晶振产生的时钟信号,作为系统的时钟源 |

以下是两个关于晶振电路原理图绘制的常见问题及解答:

1、如何选择合适的晶振负载电容?

晶振负载电容的选择应根据晶振的数据手册来确定,数据手册中会给出推荐的负载电容范围,一般选择与该范围相匹配的电容值,如果负载电容选择不当,可能会导致晶振的振荡频率不稳定或无法起振。

2、为什么在晶振电路中要添加去耦电容?

去耦电容的作用是减少电源噪声对晶振的影响,提高电源的稳定性,晶振是一个对电源噪声非常敏感的元件,电源噪声可能会干扰晶振的振荡频率,导致系统出现不稳定的情况,通过在晶振的电源引脚和地之间添加去耦电容,可以有效地滤除电源噪声,保证晶振的稳定工作。

作者:豆面本文地址:https://www.jerry.net.cn/articals/31050.html发布于 2025-02-11 23:48:18

文章转载或复制请以超链接形式并注明出处杰瑞科技发展有限公司