如何绘制74ls74图?

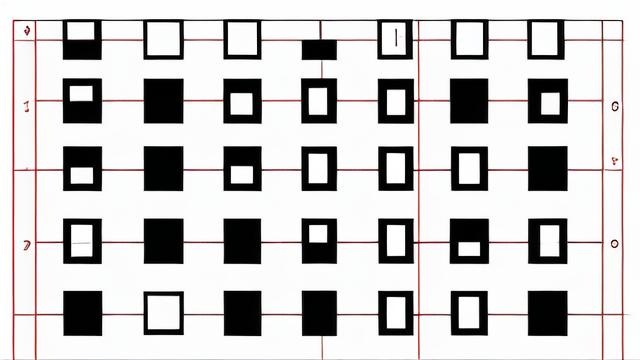

74LS74是一个双D触发器芯片,广泛应用于数字电路设计中,它包含两个独立的D触发器,每个触发器有数据输入(D)、时钟输入(CP)、主复位(MR)、从复位(SR)、输出(Q)和反相输出(Q’),以下是详细解释如何绘制74LS74的逻辑图:

一、基本概念与引脚配置

1. 基本概念

D触发器:是一种基础的数字逻辑组件,用于存储单个位的信息,它在时钟信号的上升沿或下降沿将输入D的数据传递到输出Q。

2. 引脚配置

CLR:清除输入,高电平有效,将所有触发器置零。

PR:预置输入,低电平有效,将所有触发器置一。

D0, D1:数据输入端。

CP:时钟输入端。

Q0, Q1:输出端。

GND:接地。

VCC:正电源。

二、绘制步骤

1. 确定电路功能

在绘制前,需要明确电路的功能需求,比如计数器、寄存器等。

2. 选择组件

根据功能需求选择合适的组件,如74LS74中的D触发器。

3. 连接各组件

使用导线连接各个组件,确保信号正确传递,注意区分不同的信号线,如数据线、控制线等。

4. 添加注释与标签

为电路图中的各个部分添加注释和标签,以便于理解和维护,包括组件名称、信号名称、特殊点说明等。

三、实验电路实例

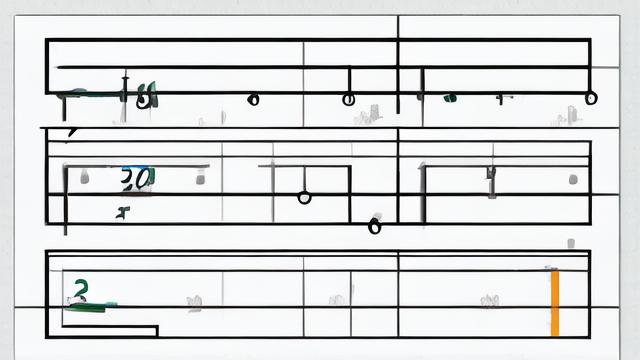

1. 异步二进制加法计数器

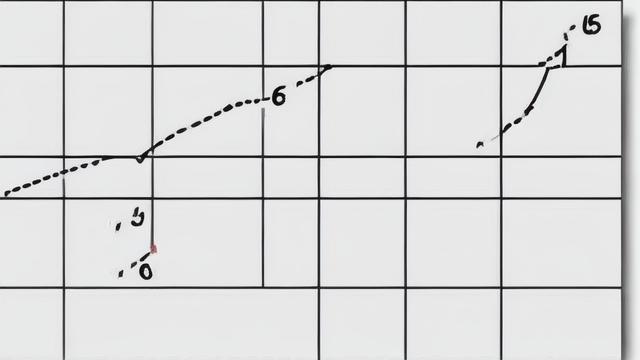

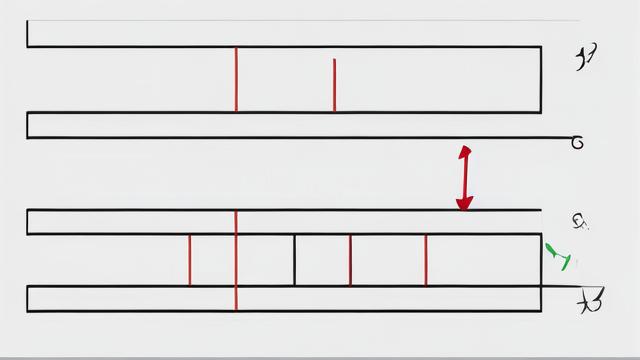

利用两个74LS74芯片可以构成一个四位二进制异步加法计数器,每个D触发器的Q非输出端连接到下一个D触发器的CP脉冲输入端,这样,当第一个触发器翻转时,它的Q非输出会产生一个上升沿脉冲,作为第二个触发器的时钟信号,依此类推。

2. 同步计数器

如果需要实现同步计数器,则需要将计数脉冲同时引入所有触发器的CP端,使得所有触发器在同一时刻翻转。

四、常见问题解答

Q1: 如何用74LS74实现一个简单的D触发器?

A1: 要实现一个简单的D触发器,可以使用74LS74中的一个D触发器,只需将数据输入D连接到所需的输入信号,时钟输入CP连接到时钟信号,输出Q即为D触发器的输出。

Q2: 如何在电路图中表示74LS74的引脚?

A2: 在电路图中,可以使用标准的符号来表示74LS74的引脚,CLR引脚可以用一个带有“CLR”标签的三角形表示,PR引脚可以用一个带有“PR”标签的三角形表示,以此类推。

通过以上步骤和示例,可以更好地理解和绘制74LS74的逻辑图,并将其应用于实际的数字电路设计中。

作者:豆面本文地址:https://www.jerry.net.cn/articals/16463.html发布于 2025-01-15 18:19:49

文章转载或复制请以超链接形式并注明出处杰瑞科技发展有限公司