基于FPGA Vivado的74LS00 IP封装流程是怎样的?

了解74LS74芯片

74LS74是一款经典的双D触发器集成电路,属于74系列的一部分,这款芯片具有低功耗肖特基特性(LS),适用于各种电子设备中的时序逻辑控制。

引脚配置:74LS74有14个引脚,采用DIP14封装,其引脚功能如下:

VCC:电源正极,为芯片提供工作电压。

GND:接地,芯片的参考零电平。

CLK:时钟输入,决定触发器状态变化的时机。

D:数据输入,用于设置触发器的状态。

Q:输出端,表示触发器的当前状态。

Q非(Q'):输出端,表示触发器的当前状态的反相。

CLR:清除输入,当该引路为低电平时,会清除触发器状态。

PR:预置输入,当该引路为低电平时,会预置触发器状态。

封装类型及工具准备

在进行74LS74的封装之前,需要选择合适的封装类型和工具,常见的封装类型包括DIP(双列直插式)、SOIC(小外形集成电路)等,本文以DIP14封装为例进行说明。

所需工具和材料:

Vivado软件或其他FPGA开发工具

74LS74芯片的数据手册

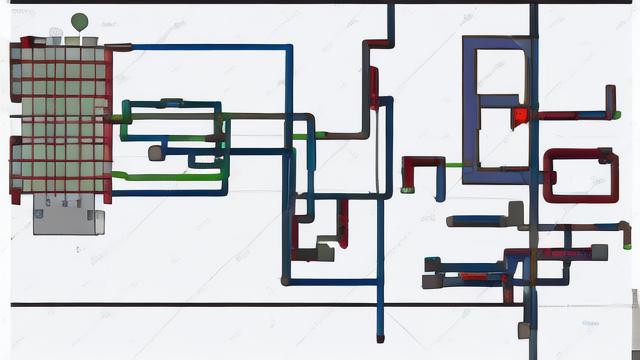

电路设计图纸或原理图

使用GUI方式封装IP

步骤1:新建工程项目

打开Vivado软件,创建一个新的RTL工程文件:

点击“Create ‘Project’”按钮,选择“RTL Project”,然后点击“Next”。

步骤2:添加源文件

在左侧的Project Manager中展开PROJECT MANAGER,选择“Add Sources”:

点击“Add or Create Design Sources”,选择“Create File”来创建一个新的源文件。

步骤3:编辑代码

双击打开新创建的文件,开始编辑代码,以74LS74 IP为例,可以编写如下代码:

module four_2_input_nand (

input wire a, b, clk,

output reg q

);

always @(posedge clk) begin

if (a & b)

q <= 0;

else

q <= 1;

end

endmodule步骤4:运行综合

保存并关闭文件,然后在Flow Navigator中点击“Run Synthesis”:

选择默认选项,点击“OK”开始综合。

步骤5:IP封装

在Tools菜单中选择“Top Tools” > “Create and Package New IP”:

按照向导完成IP封装,设置IP名称、参数和保存路径。

基于Tcl的封装流程

步骤1:进入Tcl命令行

在Vivado底部的Tcl Console中依次执行以下命令:

cd /path/to/your/workdir set ip_name 74ls74 set source_files four_2_input_nand.v set description "Four 2input NAND gate with DELAY parameter" set readme_file readme.txt set logo_file xup_ip_logo.png source ./package_ip.tcl

步骤2:运行封装脚本

完成之后,封装好的IP将保存在指定目录内。

常见问题解答

问:如何确保电源稳定?

答:在使用74LS74时,确保电源电压在4.75V到5.25V之间,避免超过绝对最大额定值,注意输入信号的正确时序和防止信号过载。

问:为什么某些配置可能会变得不稳定?

答:在设计电路时,如果预置和清除输入在不期望的操作期间变为低电平,可能会导致配置变得不稳定,必须确保这些输入在不期望的操作期间处于激活状态。

通过以上步骤,您可以成功地对74LS74芯片进行封装,并在实际应用中使用它,如果在操作过程中遇到问题,可以参考相关数据手册和设计文档,或咨询专业人士的意见。

作者:豆面本文地址:https://www.jerry.net.cn/articals/14665.html发布于 2025-01-11 11:52:17

文章转载或复制请以超链接形式并注明出处杰瑞科技发展有限公司